## ML610Q428/ML610Q429 User's Manual

Issue Date: Apr. 22, 2015

#### Notes

- 1) The information contained herein is subject to change without notice.

- 2) Although LAPIS Semiconductor is continuously working to improve product reliability and quality, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury or fire arising from failure, please take safety measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures. LAPIS Semiconductor shall have no responsibility for any damages arising out of the use of our Products beyond the rating specified by LAPIS Semiconductor.

- 3) Examples of application circuits, circuit constants and any other information contained herein are provided only to illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

- 4) The technical information specified herein is intended only to show the typical functions of the Products and examples of application circuits for the Products. No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Semiconductor or any third party with respect to the information contained in this document; therefore LAPIS Semiconductor shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) The Products are intended for use in general electronic equipment (i.e. AV/OA devices, communication, consumer systems, gaming/entertainment sets) as well as the applications indicated in this document.

- 6) The Products specified in this document are not designed to be radiation tolerant.

- 7) For use of our Products in applications requiring a high degree of reliability (as exemplified below), please contact and consult with a LAPIS Semiconductor representative: transportation equipment (i.e. cars, ships, trains), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems.

- 8) Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters.

- 9) LAPIS Semiconductor shall have no responsibility for any damages or injury arising from non-compliance with the recommended usage conditions and specifications contained herein.

- 10) LAPIS Semiconductor has used reasonable care to ensure the accuracy of the information contained in this document. However, LAPIS Semiconductor does not warrant that such information is error-free and LAPIS Semiconductor shall have no responsibility for any damages arising from any inaccuracy or misprint of such information.

- 11) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. For more details, including RoHS compatibility, please contact a ROHM sales office. LAPIS Semiconductor shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 12) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 13) This document, in part or in whole, may not be reprinted or reproduced without prior consent of LAPIS Semiconductor.

Copyright 2010 – 2015 LAPIS Semiconductor Co., Ltd.

#### LAPIS Semiconductor Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan http://www.lapis-semi.com/en/

FEUL610Q428 i

### **Preface**

This manual describes the operation of the hardware of the 8-bit microcontroller ML610Q428/ML610Q429.

The following manuals are also available. Read them as necessary.

- nX-U8/100 Core Instruction Manual Description on the basic architecture and the each instruction of the nX-U8/100 Core.

- MACU8 Assembler Package User's Manual Description on the method of operating the relocatable assembler, the librarian, and the object converter and also on the specifications of the assembler language.

- CCU8 User's Manual Description on the method of operating the compiler.

- CCU8 Programming Guide

Description on the method of programming.

- CCU8 Language Reference

Description on the language specifications.

- DTU8 Debugger User's Manual Description on the method of operating the debugger DTU8.

- IDEU8 User's Manual Description on the integrated development environment IDEU8.

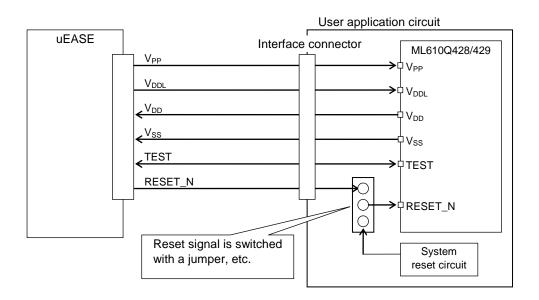

- uEASE User's Manual Description on the on-chip debug tool uEASE.

- uEASE connection Manual

Description about the connection between uEASE and ML610Qxxx.

- FWuEASE Flash Writer Host Program User's Manual Description on the Flash Writer host program.

FEUL610Q428 ii

### **Notation**

| Classification Notation |                                                                                                          | Description                                                                                                                                                                                                          |  |

|-------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ◆ Numeric value         | xxh, xxH<br>xxb                                                                                          | Indicates a hexadecimal number. x: Any value in the range of 0 to F Indicates a binary number; "b" may be omitted. x: A value 0 or 1                                                                                 |  |

| ♦ Unit                  | word, W byte, B nibble, N mega-, M kilo-, K kilo-, k milli-, m micro-, µ nano-, n second, s (lower case) | 1 word = 16 bits<br>1 byte = 8 bits<br>1 nibble = 4 bits<br>$10^6$<br>$2^{10} = 1024$<br>$10^3 = 1000$<br>$10^{-3}$<br>$10^{-6}$<br>$10^{-9}$<br>second                                                              |  |

| ◆ Terminology           | "H" level, "1" level "L" level, "0" level                                                                | Indicates high voltage signal levels $V_{IH}$ and $V_{OH}$ as specified by the electrical characteristics. Indicates low voltage signal levels $V_{IL}$ and $V_{OL}$ as specified by the electrical characteristics. |  |

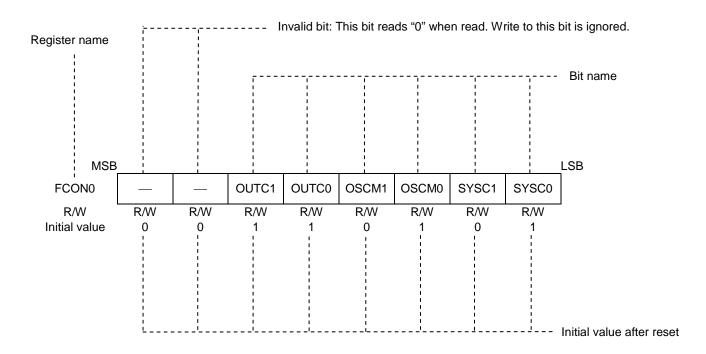

#### ♦ Register description

R/W: Indicates that Read/Write attribute. "R" indicates that data can be read and "W" indicates that data can be written. "R/W" indicates that data can be read or written.

FEUL610Q428 iii

| Table of Contents                                           |      |

|-------------------------------------------------------------|------|

| Chapter 1                                                   |      |

|                                                             |      |

| 1. Overview                                                 |      |

| 1.1 Features                                                |      |

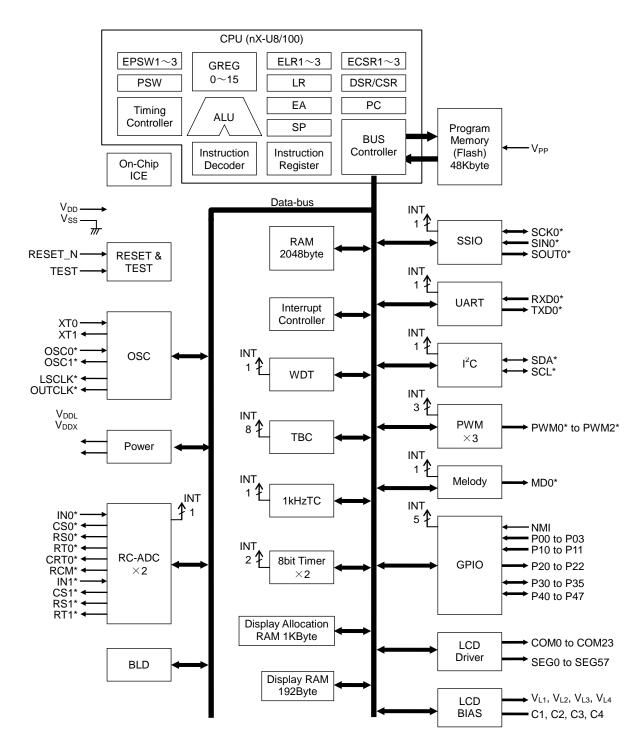

| 1.2.1 Block Diagram of ML610Q428                            |      |

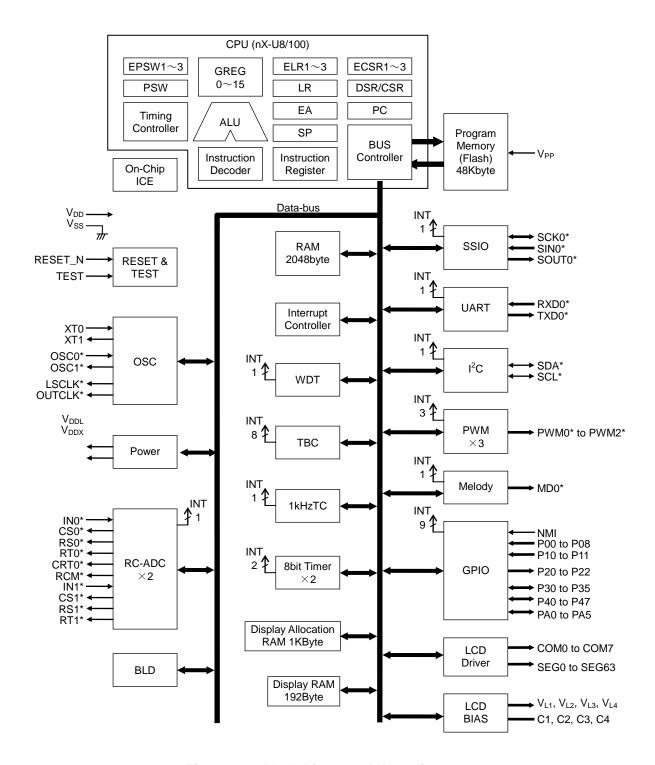

| 1.2.2 Block Diagram of ML610Q429                            |      |

| 1.3 Pins                                                    |      |

| 1.3.1 Pin Layout                                            |      |

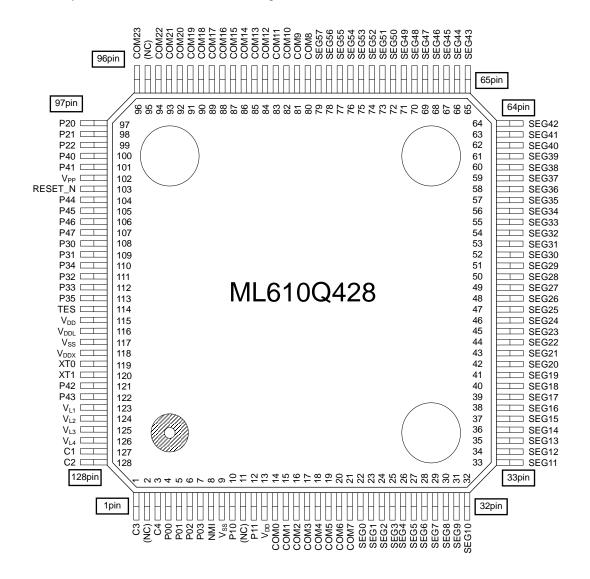

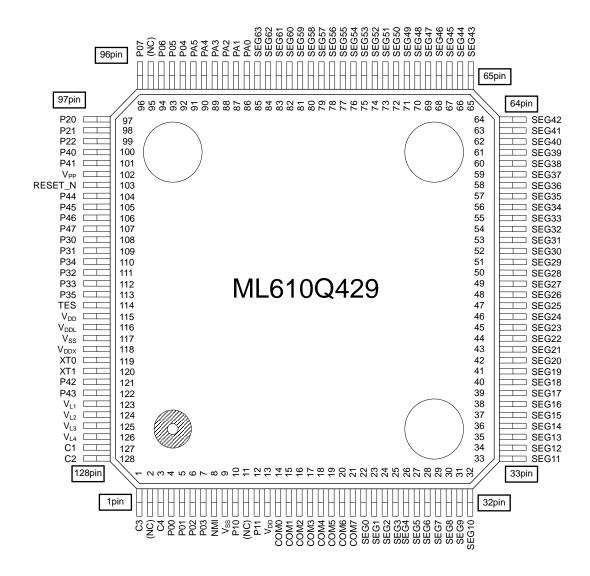

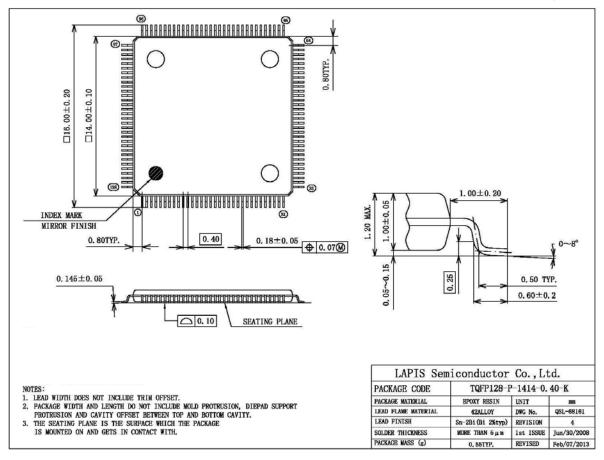

| 1.3.1.1 Pin Layout of ML610Q428 LQFP Package                |      |

| 1.3.1.2 Pin Layout of ML610Q429 LQFP Package                |      |

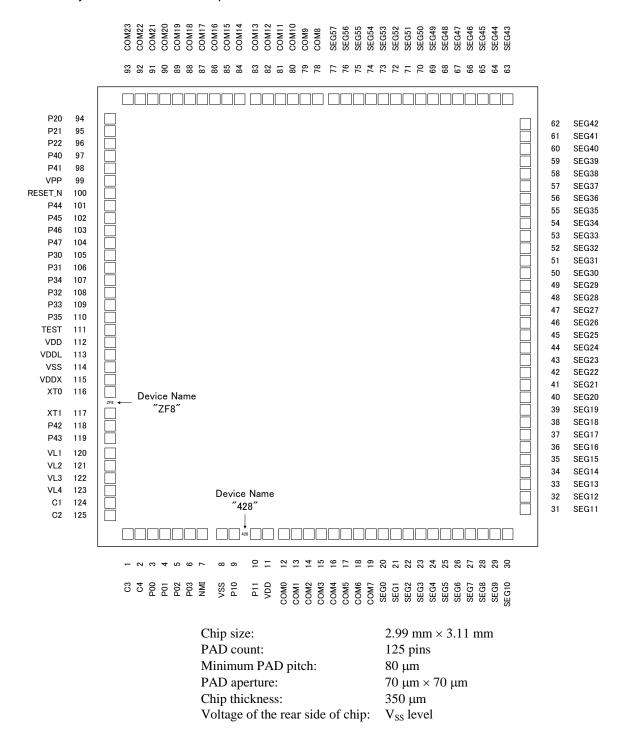

| 1.3.1.3 Pin Layout of ML610Q428 Chip                        |      |

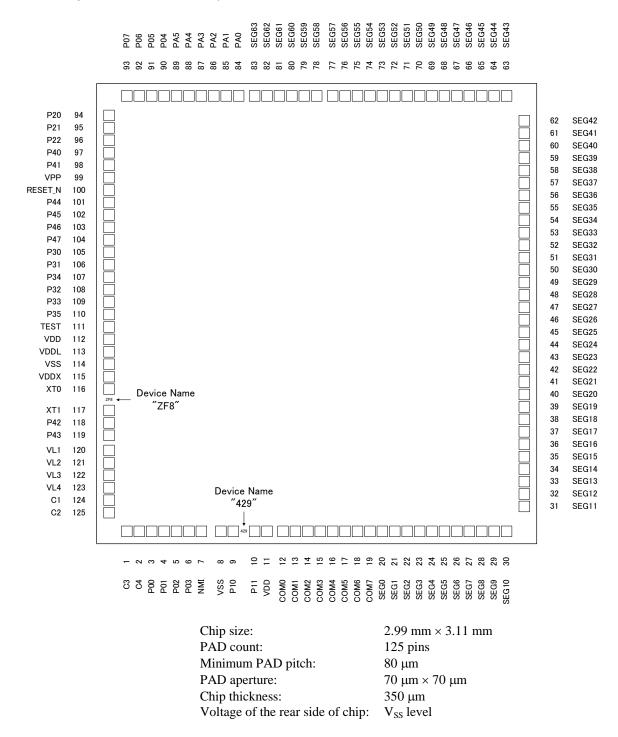

| 1.3.1.4 Pin Layout of ML610Q429 Chip                        |      |

| 1.3.1.5 Pad Coordinates of ML610Q428 Chip                   |      |

| 1.3.1.6 Pad Coordinates of ML610Q429 Chip                   |      |

| 1.3.2 List of Pins                                          |      |

| 1.3.3 Description of Pins                                   |      |

| 1.3.4 Termination of Unused Pins                            |      |

| 1.3.5 The main difference points of ML610Q428 and ML610Q429 | 1-20 |

| Chapter 2                                                   |      |

| 2. CPU and Memory Space                                     | 2-1  |

| 2.1 Overview                                                |      |

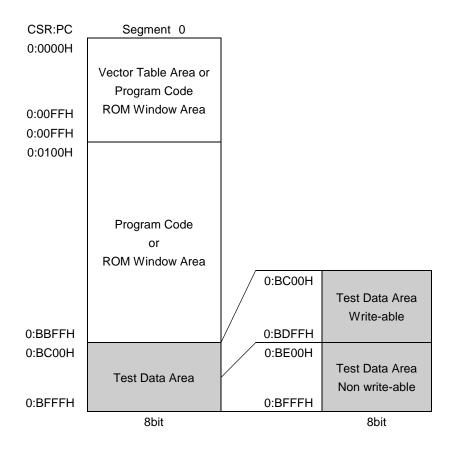

| 2.2 Program Memory Space                                    |      |

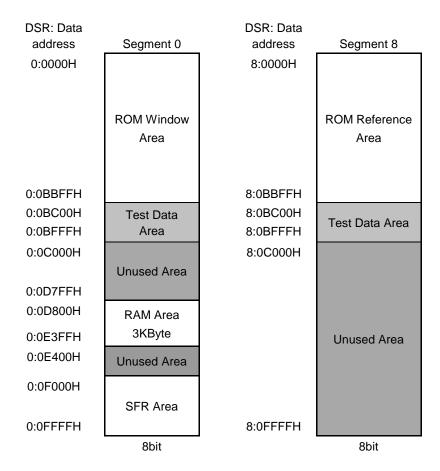

| 2.3 Data Memory Space                                       |      |

| 2.4 Instruction Length                                      |      |

| 2.5 Data Type                                               |      |

| 2.6 Description of Registers                                |      |

| 2.6.1 List of Registers                                     |      |

| 2.6.2 Data Segment Register (DSR)                           | 2-4  |

| Chapter 3                                                   |      |

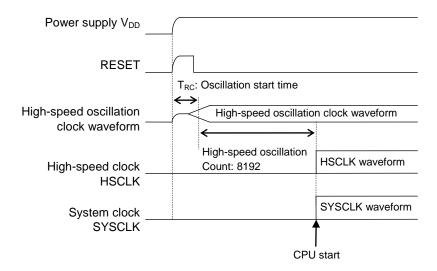

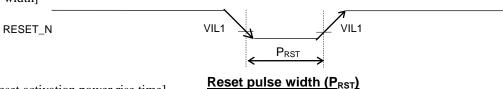

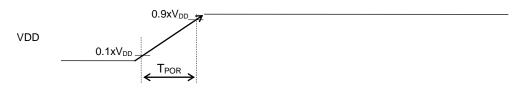

| 3. Reset Function                                           | 3-1  |

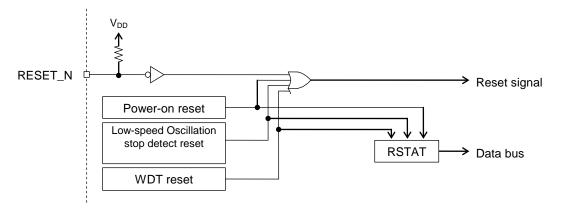

| 3.1 Overview                                                | 3-1  |

| 3.1.1 Features                                              | 3-1  |

| 3.1.2 Configuration                                         |      |

| 3.1.3 List of Pin                                           |      |

| 3.2 Description of Registers                                |      |

| 3.2.1 List of Registers                                     |      |

| 3.2.2 Reset Status Register (RSTAT)                         |      |

| 3.3 Description of Operation                                |      |

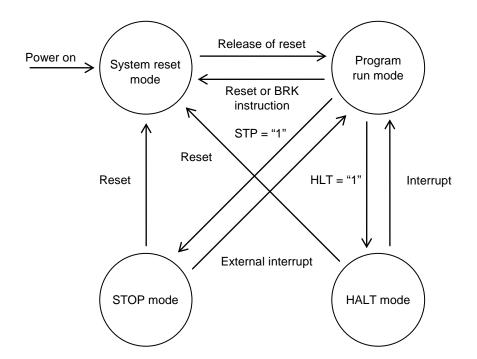

| 3.3.1 Operation of System Reset Mode                        | 3-3  |

| Chapter 4                                                   |      |

| 4. MCU Control Function                                     | 4-1  |

| 4.1 Overview                                                |      |

| 4.1.1 Features                                              |      |

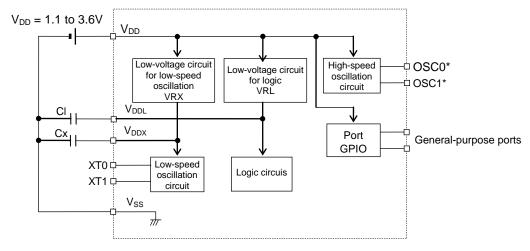

| 4.1.2 Configuration                                         |      |

| 4.2 Description of Registers                                |      |

| 4.2.1 List of Registers                                     |      |

| 4.2.2 Stop Code Acceptor (STPACP)                           | 4-3  |

Block Control Register 0 (BLKCON0).......4-5

4.2.3 4.2.4

4.2.5

| 4.2.6          | Block Control Register 2 (BLKCON2)                 |      |

|----------------|----------------------------------------------------|------|

| 4.2.7          | Block Control Register 3 (BLKCON3)                 | 4-8  |

| 4.2.8          | Block Control Register 4 (BLKCON4)                 | 4-9  |

| 4.3 De         | escription of Operation                            | A 11 |

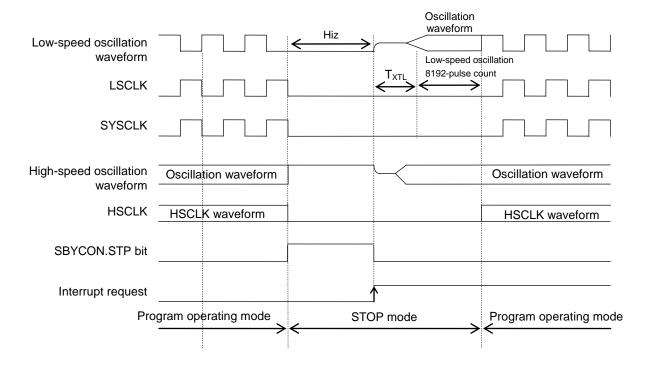

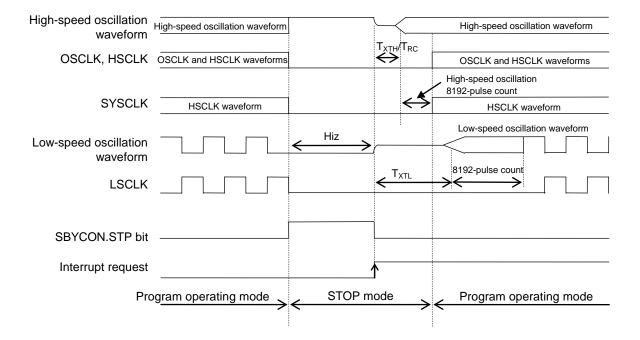

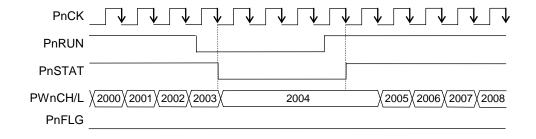

| 4.3 De         | Program Run Mode                                   |      |

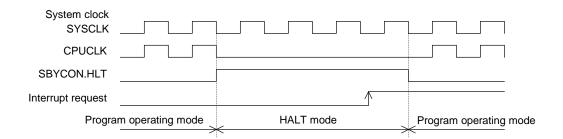

| 4.3.1          | e e e e e e e e e e e e e e e e e e e              |      |

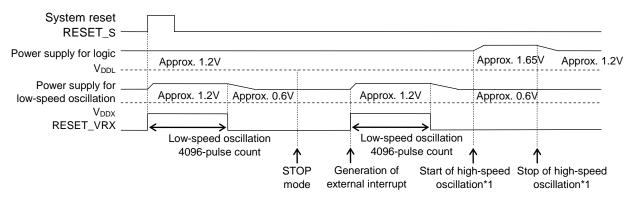

| 4.3.2          | HALT ModeSTOP Mode                                 |      |

| 4.3.3          |                                                    |      |

| 4.3.3          |                                                    |      |

| 4.3.3          |                                                    |      |

| 4.3.3          | Block Control Function                             |      |

|                |                                                    | 1 10 |

| Chapter 5      |                                                    |      |

|                | rupts (INTs)                                       |      |

| 5.1 Ov         | verview                                            |      |

| 5.1.1          | Features                                           |      |

| 5.2 De         | escription of Registers                            | 5-2  |

| 5.2.1          | List of Registers                                  | 5-2  |

| 5.2.2          | Interrupt Enable Register 1 (IE1)                  | 5-3  |

| 5.2.3          | Interrupt Enable Register 2 (IE2)                  | 5-5  |

| 5.2.4          | Interrupt Enable Register 3 (IE3)                  | 5-6  |

| 5.2.5          | Interrupt Enable Register 4 (IE4)                  | 5-7  |

| 5.2.6          | Interrupt Enable Register 6 (IE6)                  | 5-8  |

| 5.2.7          | Interrupt Enable Register 7 (IE7)                  | 5-10 |

| 5.2.8          | Interrupt Request Register 0 (IRQ0)                | 5-11 |

| 5.2.9          | Interrupt Request Register 1 (IRQ1)                | 5-12 |

| 5.2.10         | Interrupt Request Register 2 (IRQ2)                | 5-14 |

| 5.2.11         | Interrupt Request Register 3 (IRQ3)                | 5-15 |

| 5.2.12         | Interrupt Request Register 4 (IRQ4)                | 5-16 |

| 5.2.13         | Interrupt Request Register 6 (IRQ6)                | 5-17 |

| 5.2.14         | Interrupt Request Register 7 (IRQ7)                |      |

| 5.3 De         | escription of Operation                            |      |

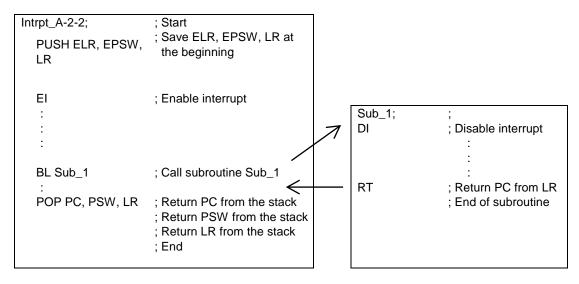

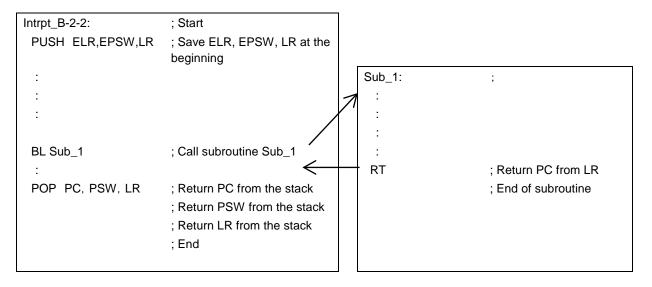

| 5.3.1          | Maskable Interrupt Processing                      |      |

| 5.3.2          | Non-Maskable Interrupt Processing                  |      |

| 5.3.3          | Software Interrupt Processing                      |      |

| 5.3.4          | Notes on Interrupt Routine                         |      |

| 5.3.5          | Interrupt Disable State                            |      |

| Chapter 6      |                                                    |      |

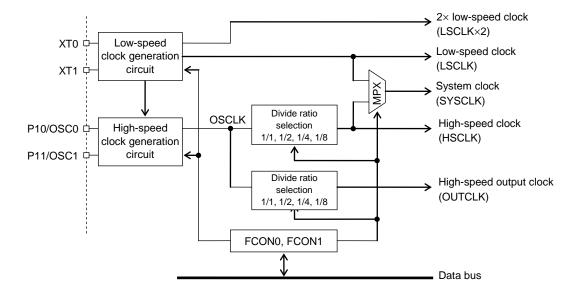

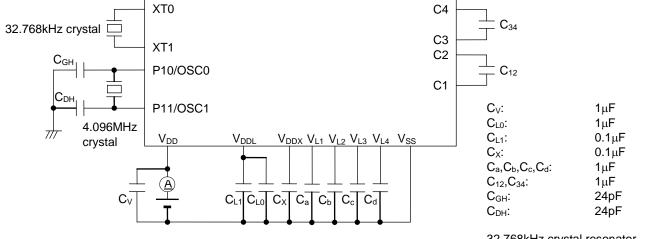

|                | k Generation Circuit                               | 6-1  |

|                | /erview                                            |      |

| 6.1.1          | Features                                           |      |

| 6.1.2          | Configuration                                      |      |

| 6.1.3          | List of Pins                                       |      |

|                | escription of Registers                            |      |

| 6.2.1          | List of Registers                                  |      |

| 6.2.2          | Frequency Control Register 0 (FCON0)               |      |

| 6.2.3          | Frequency Control Register 1 (FCON1)               |      |

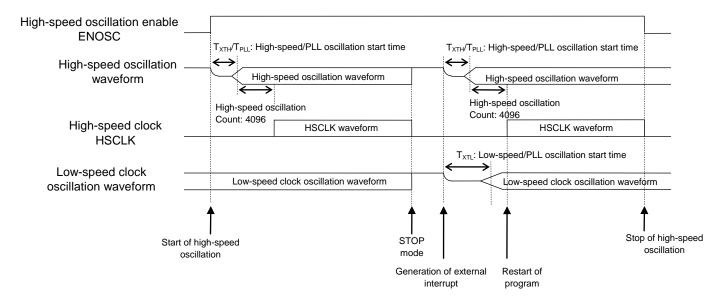

|                | escription of Operation                            |      |

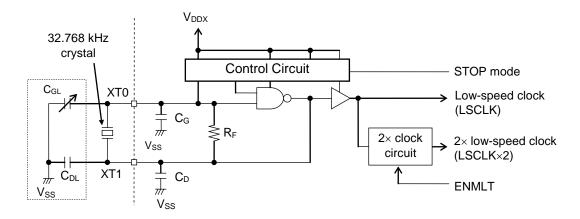

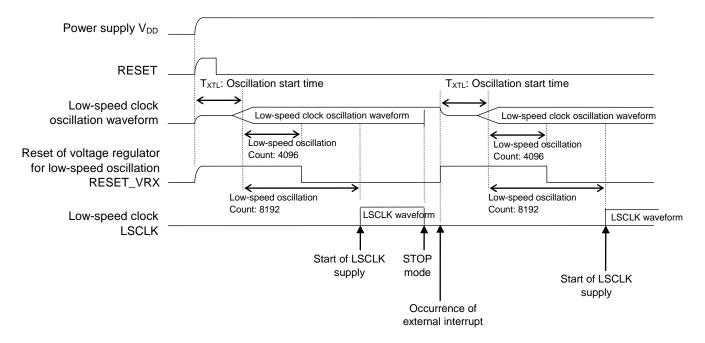

| 6.3.1          | Low-Speed Clock                                    |      |

| 6.3.1          | *                                                  |      |

|                | 1                                                  |      |

| 6.3.1<br>6.3.2 | .2 Operation of Low-Speed Clock Generation Circuit |      |

|                |                                                    |      |

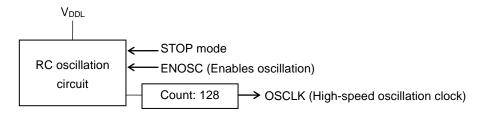

| 6.3.2          |                                                    |      |

| 6.3.2          | ·                                                  |      |

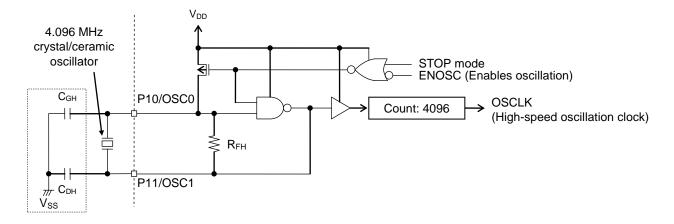

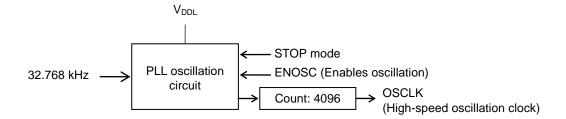

| 6.3.2          | .3 Built-in PLL Oscillation Mode                   | 6-10 |

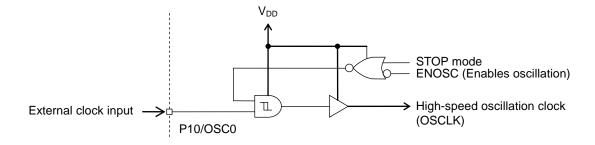

| 6.3.2.4 External Clock Input Mode                                        |      |

|--------------------------------------------------------------------------|------|

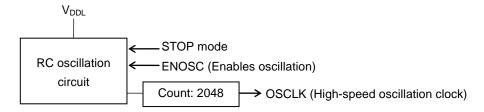

| 6.3.2.5 2 MHz RC Oscillation                                             |      |

| 6.3.2.6 Operation of High-Speed Clock Generation Circuit                 |      |

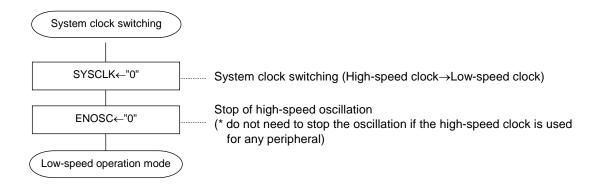

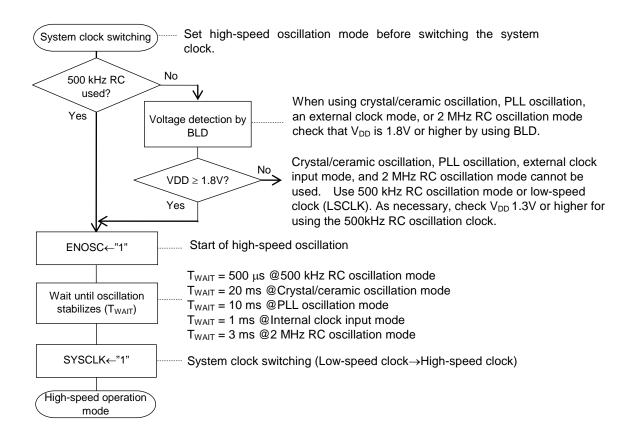

| 6.3.3 Switching of System Clock                                          |      |

| 6.4 Specifying port registers                                            |      |

| 6.4.1 Functioning P21 (OUTCLK) as the high speed clock output            |      |

| 6.4.2 Functioning P22 (LSCLK) as the low speed clock output              | 6-1/ |

| Chapter 7                                                                |      |

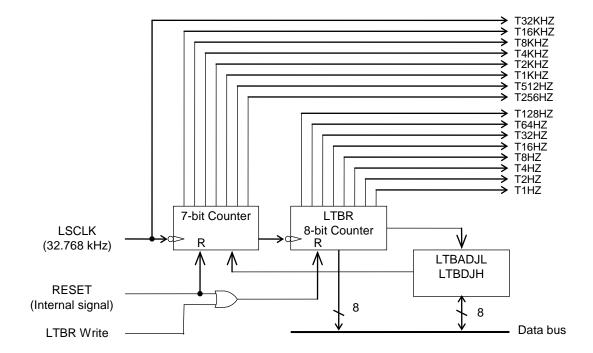

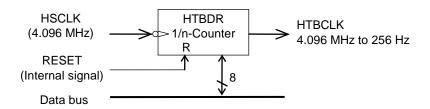

| 7. Time Base Counter                                                     |      |

| 7.1 Overview                                                             |      |

| 7.1.1 Features                                                           |      |

| 7.1.2 Configuration                                                      |      |

| 7.2 Description of Registers 7.2.1 List of Registers                     |      |

| 7.2.2 Low-Speed Time Base Counter (LTBR)                                 |      |

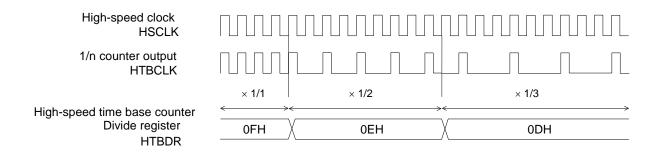

| 7.2.3 High-Speed Time Base Counter Divide Register (HTBDR)               |      |

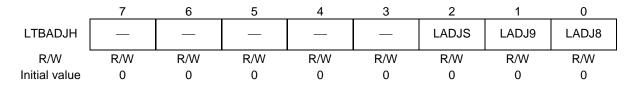

| 7.2.4 Low-Speed Time Base Counter Frequency Adjustment Registers L and H |      |

| (LTBADJL, LTBADJH)                                                       | 7-6  |

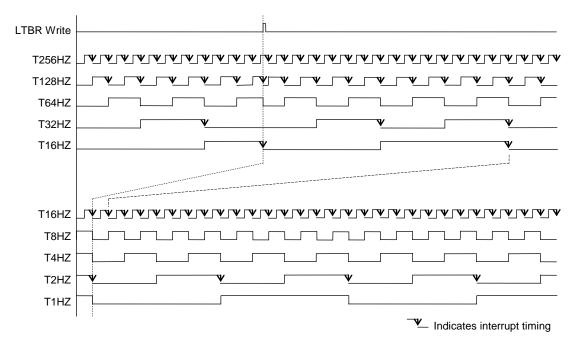

| 7.3 Description of Operation.                                            |      |

| 7.3.1 Low-Speed Time Base Counter                                        |      |

| 7.3.2 High-Speed Time Base Counter                                       |      |

| 7.3.3 Low-Speed Time Base Counter Frequency Adjustment Function          | 7-9  |

| Chapter 8                                                                |      |

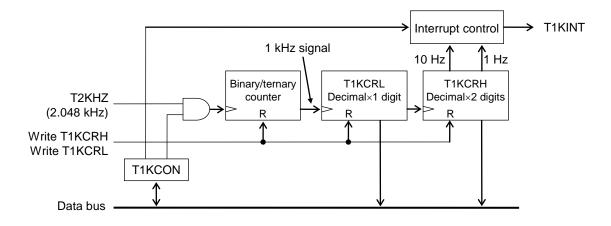

| 8. 1 kHz Timer (1kHzTM)                                                  | 8-1  |

| 8.1 Overview                                                             |      |

| 8.1.1 Features                                                           |      |

| 8.1.2 Configuration                                                      | 8-1  |

| 8.2 Description of Registers                                             | 8-2  |

| 8.2.1 List of Registers                                                  |      |

| 8.2.2 1 kHz Timer Count Registers (T1KCRL, T1KCRH)                       |      |

| 8.2.3 1 kHz Timer Control Register (T1KCON)                              |      |

| 8.3 Description of Operation                                             | 8-5  |

| Chapter 9                                                                |      |

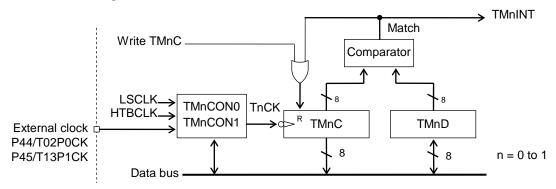

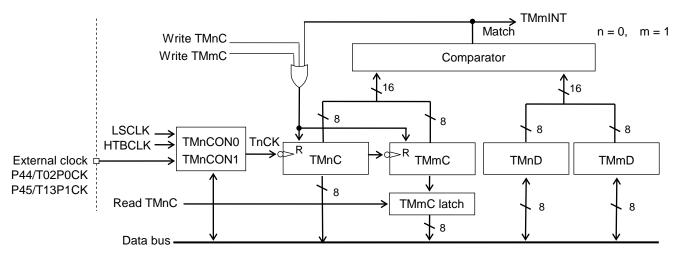

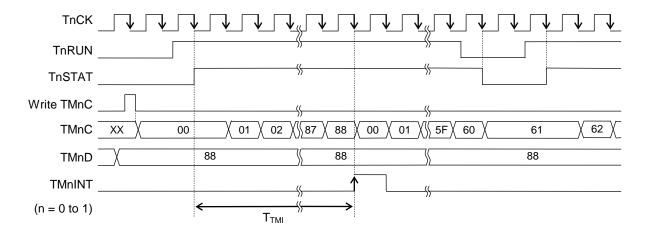

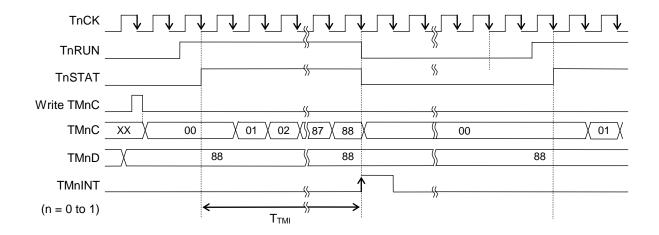

| 9. Timers                                                                | 9-1  |

| 9.1 Overview                                                             |      |

| 9.1.1 Features                                                           | 9-1  |

| 9.1.2 Configuration                                                      | 9-1  |

| 9.2 Description of Registers                                             | 9-2  |

| 9.2.1 List of Registers                                                  |      |

| 9.2.2 Timer 0 Data Register (TM0D)                                       |      |

| 9.2.3 Timer 1 Data Register (TM1D)                                       |      |

| 9.2.4 Timer 0 Counter Register (TM0C)                                    |      |

| 9.2.5 Timer 1 Counter Register (TM1C)                                    |      |

| 9.2.6 Timer 0 Control Register 0 (TM0CON0)                               |      |

| 9.2.7 Timer 1 Control Register 0 (TM1CON0)                               |      |

| 9.2.8 Timer 0 Control Register 1 (TM0CON1)                               |      |

| 9.2.9 Timer 1 Control Register 1 (TM1CON1)                               |      |

| Chapter 10                                                               |      |

|                                                                          | 10.1 |

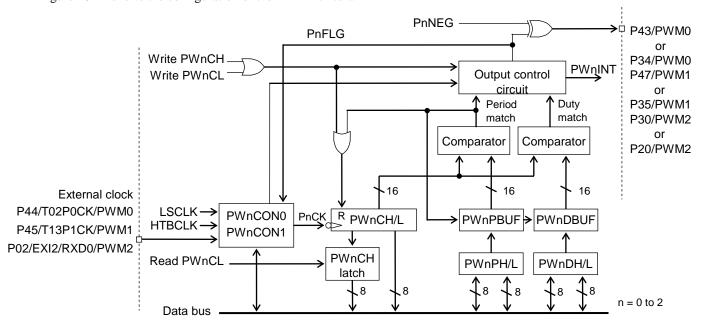

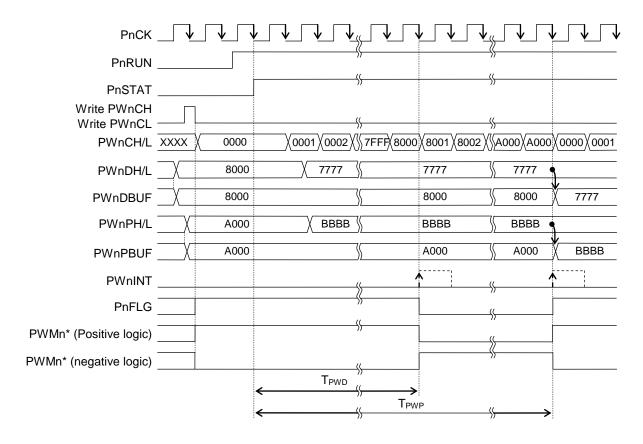

| 10. PWM                                                                  |      |

| 10.1 Overview                                                            |      |

| 10.1.1 Features                                                          | 10-1 |

| 10.1.2      | Configuration                                                                 | 10-1  |

|-------------|-------------------------------------------------------------------------------|-------|

| 10.1.3 I    | ist of Pins                                                                   | 10-2  |

| 10.2 Descr  | iption of Registers                                                           | 10-2  |

|             | List of Registers                                                             |       |

|             | PWM0 Period Registers (PW0PL, PW0PH)                                          |       |

|             | PWM1 Period Registers (PW1PL, PW1PH)                                          |       |

|             | PWM2 Period Registers (PW2PL, PW2PH)                                          |       |

|             | PWM0 Duty Registers (PW0DL, PW0DH)                                            |       |

|             | PWM1 Duty Registers (PW1DL, PW1DH)                                            |       |

|             | PWM2 Duty Registers (PW2DL, PW2DH)                                            |       |

|             | PWM0 Counter Registers (PW0CH, PW0CL)                                         |       |

|             | PWM1 Counter Registers (PW1CH, PW1CL)                                         |       |

|             | PWM2 Counter Registers (PW2CH, PW2CL)                                         |       |

|             | PWM0 Control Register 0 (PW0CON0)                                             |       |

|             |                                                                               |       |

|             | PWM1 Control Register 0 (PW1CON0)                                             |       |

|             | PWM2 Control Register 0 (PW2CON0)                                             |       |

|             | PWM0 Control Register 1 (PW0CON1)                                             |       |

|             | PWM1 Control Register 1 (PW1CON1)                                             |       |

|             | PWM2 Control Register 1 (PW2CON1)                                             |       |

|             | iption of Operation                                                           |       |

|             | fying port registers                                                          |       |

|             | Functioning P43 (PWM0) as the PWM0 output                                     |       |

|             | Functioning P34 (PWM0) as the PWM0 output                                     |       |

|             | Functioning P47 (PWM1) as the PWM1 output                                     |       |

| 10.4.4 l    | Functioning P35 (PWM1) as the PWM1 output                                     | 10-23 |

| 10.4.5 I    | Functioning P20 (PWM2) as the PWM2 output                                     | 10-24 |

| 10.4.6 I    | Functioning P30 (PWM2) as the PWM2 output                                     | 10-25 |

| Chapter 11  |                                                                               |       |

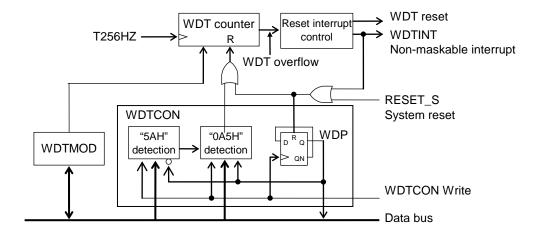

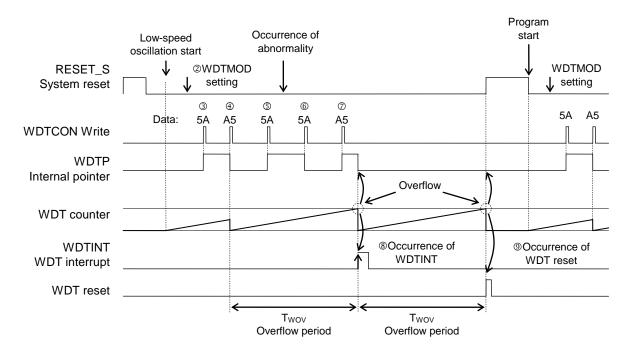

| 11. Watchdo | og Timer                                                                      | 11-1  |

| 11.1 Overv  | <i>i</i> ew                                                                   | 11-1  |

| 11.1.1 I    | Features                                                                      | 11-1  |

| 11.1.2      | Configuration                                                                 | 11-1  |

| 11.2 Descr  | iption of Registers                                                           | 11-2  |

| 11.2.1 I    | List of Registers                                                             | 11-2  |

| 11.2.2      | Watchdog Timer Control Register (WDTCON)                                      | 11-3  |

|             | Watchdog Timer Mode Register (WDTMOD)                                         |       |

|             | iption of Operation                                                           |       |

| Chapter 12  | •                                                                             |       |

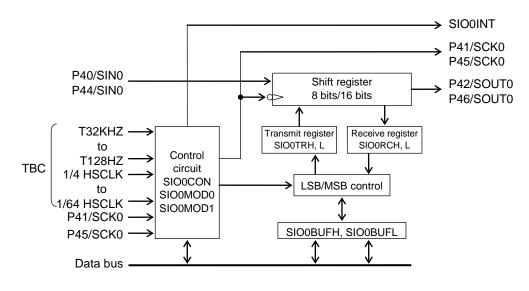

| 12 Cymahra  | nous Serial Port                                                              | 12.1  |

| •           | riew                                                                          |       |

|             |                                                                               |       |

|             | Features                                                                      |       |

|             | Configuration                                                                 |       |

|             | List of Pins                                                                  |       |

|             | iption of Registers                                                           |       |

|             | List of Registers                                                             |       |

|             | Serial Port Transmit/Receive Buffers (SIO0BUFL, SIO0BUFH)                     |       |

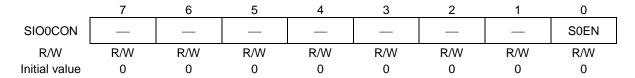

|             | Serial Port Control Register (SIOOCON)                                        |       |

|             | Serial Port Mode Register 0 (SIO0MOD0)                                        |       |

|             | Serial Port Mode Register 1 (SIO0MOD1)                                        |       |

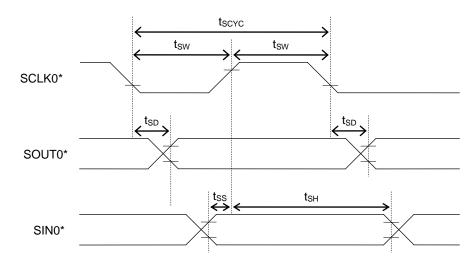

|             | iption of Operation                                                           |       |

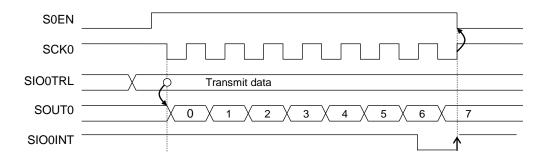

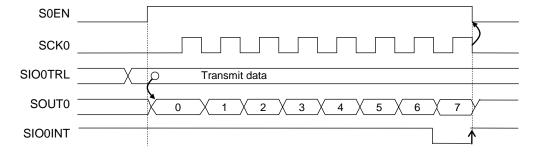

|             | Transmit Operation                                                            |       |

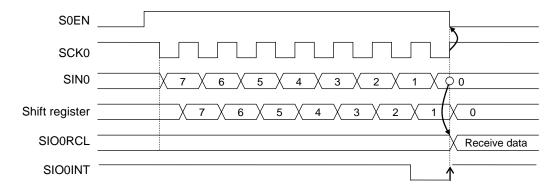

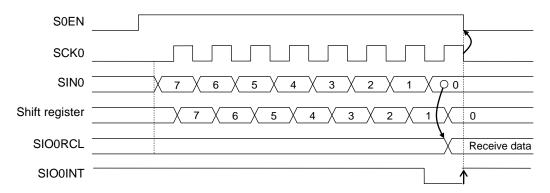

|             | Receive Operation                                                             |       |

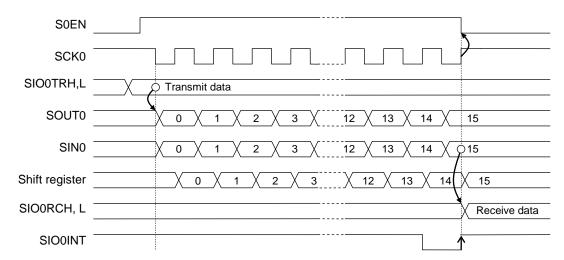

|             | Fransmit/Receive Operation                                                    |       |

|             | fying port registers                                                          |       |

| 12.4.1 I    | Functioning P42 (SOUT0), P41 (SCK0) and P40 (SIN0) as the SSIO/ "Master mode" | 12-11 |

$\begin{array}{c} ML610Q428/ML610Q429 \; User's \; Manual \\ Contents \end{array}$

| 12.4.2<br>12.4.3<br>12.4.4                                                                                                                                                                                                                     | Functioning P42 (SOUT0), P41 (SCK0) and P40 (SIN0) as the SSIO/ "Slave mode"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12-13<br>12-14                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

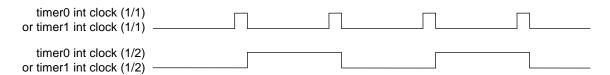

| 12.5 Ab                                                                                                                                                                                                                                        | out timer0/1 int clock for the transfer clock of the synchronous serial port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12-15                                    |

| Chapter 1                                                                                                                                                                                                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                          |

| 13. UAR'                                                                                                                                                                                                                                       | Γ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13-1                                     |

| 13.1 Ov                                                                                                                                                                                                                                        | erview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13-1                                     |

| 13.1.1                                                                                                                                                                                                                                         | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13-1                                     |

| 13.1.2                                                                                                                                                                                                                                         | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13-1                                     |

| 13.1.3                                                                                                                                                                                                                                         | List of Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13-1                                     |

| 13.2 De                                                                                                                                                                                                                                        | scription of Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13-2                                     |

| 13.2.1                                                                                                                                                                                                                                         | List of Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                          |

| 13.2.2                                                                                                                                                                                                                                         | UART0 Transmit/Receive Buffer (UA0BUF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                          |

| 13.2.3                                                                                                                                                                                                                                         | UART0 Control Register (UA0CON)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                          |

| 13.2.4                                                                                                                                                                                                                                         | UART0 Mode Register 0 (UA0MOD0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                          |

| 13.2.5                                                                                                                                                                                                                                         | UART0 Mode Register 1 (UA0MOD1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                          |

| 13.2.6                                                                                                                                                                                                                                         | UARTO Baud Rate Registers L, H (UAOBRTL, UAOBRTH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                          |

| 13.2.7                                                                                                                                                                                                                                         | UART0 Status Register (UA0STAT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                          |

| 13.3 De                                                                                                                                                                                                                                        | scription of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                          |

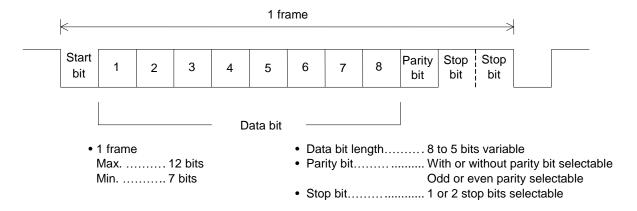

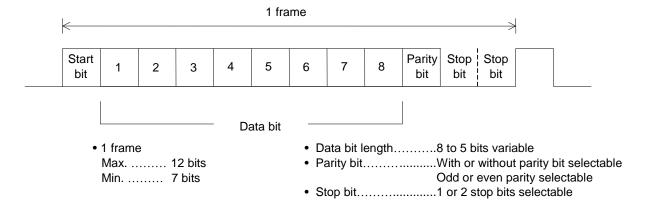

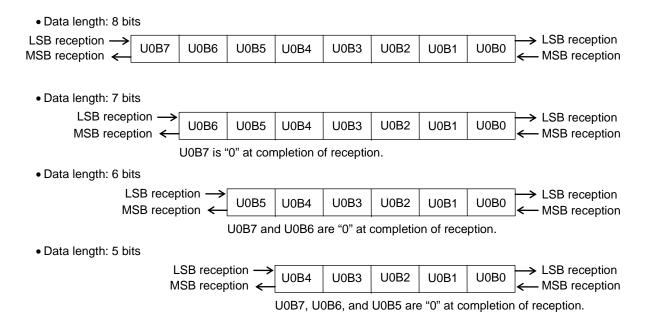

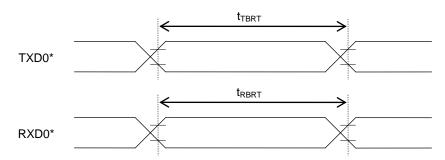

| 13.3.1                                                                                                                                                                                                                                         | Transfer Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                          |

| 13.3.2                                                                                                                                                                                                                                         | Baud Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                          |

| 13.3.3                                                                                                                                                                                                                                         | Transmit Data Direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                          |

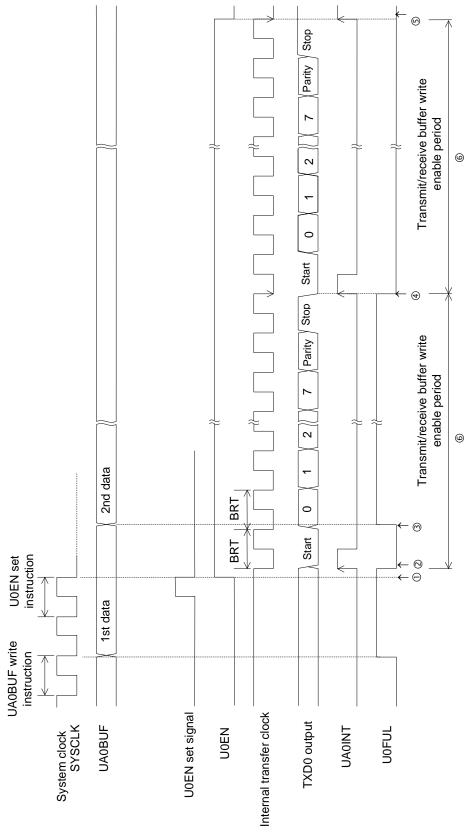

| 13.3.4                                                                                                                                                                                                                                         | Transmit Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                          |

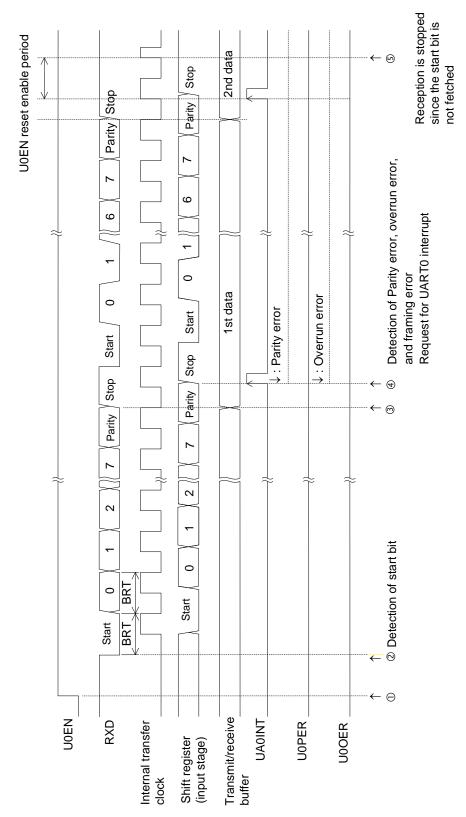

| 13.3.5                                                                                                                                                                                                                                         | Receive Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                          |

| _                                                                                                                                                                                                                                              | cifying port registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                          |

| 13.4.1<br>13.4.2                                                                                                                                                                                                                               | Functioning P43(TXD0) and P42(RXD0) as the UART  Functioning P43(TXD0) and P02(RXD0) as the UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                          |

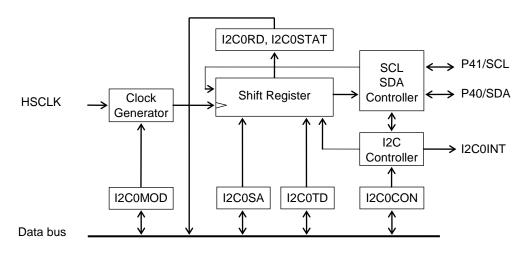

| Chapter 14. I <sup>2</sup> C B                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                          |

| 14.1 Ov                                                                                                                                                                                                                                        | ıs Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14-1                                     |

| 14.1.1                                                                                                                                                                                                                                         | erview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14-1                                     |

|                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14-1                                     |

| 14.1.2                                                                                                                                                                                                                                         | erview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14-1<br>14-1                             |

| 14.1.2<br>14.1.3                                                                                                                                                                                                                               | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14-1<br>14-1<br>14-1                     |

| 14.1.2<br>14.1.3                                                                                                                                                                                                                               | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14-1<br>14-1<br>14-1<br>14-2             |

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1                                                                                                                                                                                                          | Features Configuration List of Pins scription of Registers List of Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14-114-114-114-214-2                     |

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2                                                                                                                                                                                                | Features Configuration List of Pins cription of Registers List of Registers I <sup>2</sup> C Bus 0 Receive Register (I2C0RD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14-114-114-114-214-2                     |

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2<br>14.2.3                                                                                                                                                                                      | Perview  Features  Configuration  List of Pins  scription of Registers  List of Registers  I²C Bus 0 Receive Register (I2C0RD)  I²C Bus 0 Slave Address Register (I2C0SA)                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14-114-114-114-214-314-4                 |

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4                                                                                                                                                                            | Prestures  Configuration  List of Pins  Coription of Registers  List of Registers  I²C Bus 0 Receive Register (I2C0RD)  I²C Bus 0 Slave Address Register (I2C0SA)  I²C Bus 0 Transmit Data Register (I2C0TD)                                                                                                                                                                                                                                                                                                                                                                                                | 14-114-114-114-214-314-4                 |

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5                                                                                                                                                                  | Features Configuration List of Pins Coription of Registers List of Registers I²C Bus 0 Receive Register (I2C0RD) I²C Bus 0 Slave Address Register (I2C0SA) I²C Bus 0 Transmit Data Register (I2C0TD) I²C Bus 0 Control Register (I2C0CON)                                                                                                                                                                                                                                                                                                                                                                   | 14-114-114-214-314-514-6                 |

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6                                                                                                                                                        | Features Configuration List of Pins Coription of Registers List of Registers I²C Bus 0 Receive Register (I2C0RD) I²C Bus 0 Slave Address Register (I2C0SA) I²C Bus 0 Transmit Data Register (I2C0TD) I²C Bus 0 Control Register (I2C0CON) I²C Bus 0 Mode Register (I2C0MOD)                                                                                                                                                                                                                                                                                                                                 | 14-114-114-214-314-514-7                 |

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>14.2.7                                                                                                                                              | Features Configuration List of Pins Scription of Registers List of Registers I^2C Bus 0 Receive Register (I2C0RD) I^2C Bus 0 Slave Address Register (I2C0SA) I^2C Bus 0 Transmit Data Register (I2C0TD) I^2C Bus 0 Control Register (I2C0CON) I^2C Bus 0 Mode Register (I2C0MOD) I^2C Bus 0 Status Register (I2C0STAT)                                                                                                                                                                                                                                                                                      | 14-114-114-214-314-514-714-8             |

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>14.2.7<br>14.3 De                                                                                                                                   | Features Configuration List of Pins Coription of Registers List of Registers I <sup>2</sup> C Bus 0 Receive Register (I2C0RD) I <sup>2</sup> C Bus 0 Slave Address Register (I2C0SA) I <sup>2</sup> C Bus 0 Transmit Data Register (I2C0TD) I <sup>2</sup> C Bus 0 Control Register (I2C0CON) I <sup>2</sup> C Bus 0 Status Register (I2C0MOD) I <sup>2</sup> C Bus 0 Status Register (I2C0STAT) Coription of Operation                                                                                                                                                                                     | 14-114-114-214-314-514-614-814-9         |

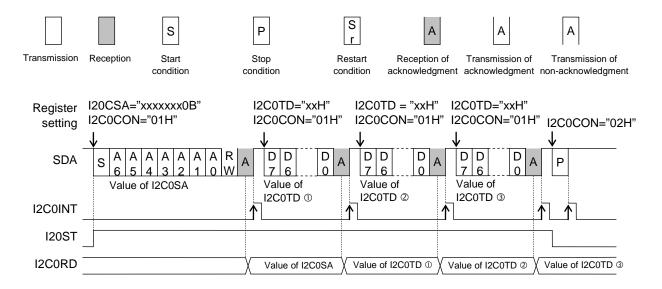

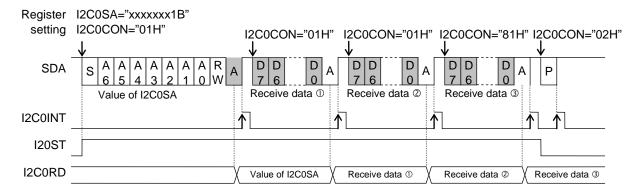

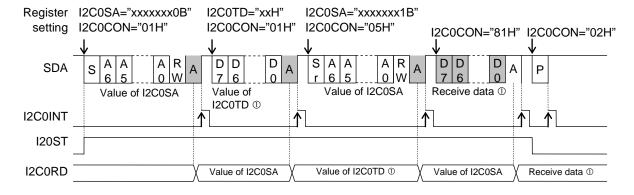

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>14.2.7<br>14.3 De<br>14.3.1                                                                                                                         | Features Configuration List of Pins coription of Registers List of Registers I²C Bus 0 Receive Register (I2C0RD) I²C Bus 0 Slave Address Register (I2C0SA) I²C Bus 0 Transmit Data Register (I2C0TD) I²C Bus 0 Control Register (I2C0CON) I²C Bus 0 Status Register (I2C0MOD) I²C Bus 0 Status Register (I2C0STAT) coription of Operation. Communication Operating Mode                                                                                                                                                                                                                                     | 14-114-114-114-214-314-614-714-9         |

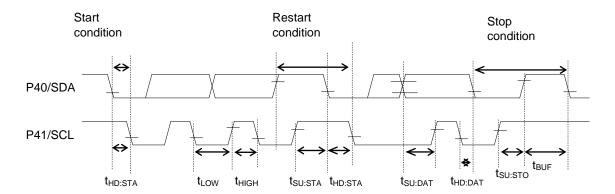

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>14.2.7<br>14.3 De<br>14.3.1<br>14.3.1                                                                                                               | Features Configuration List of Pins Coription of Registers List of Registers I²C Bus 0 Receive Register (I2C0RD) I²C Bus 0 Slave Address Register (I2C0SA) I²C Bus 0 Transmit Data Register (I2C0TD) I²C Bus 0 Control Register (I2C0CON) I²C Bus 0 Mode Register (I2C0MOD) I²C Bus 0 Status Register (I2C0STAT) Corription of Operation Communication Operating Mode  1 Start Condition                                                                                                                                                                                                                    | 14-114-114-114-214-314-414-514-714-914-9 |

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>14.2.7<br>14.3 De<br>14.3.1<br>14.3.1                                                                                                               | Features Configuration List of Pins Corription of Registers List of Registers I²C Bus 0 Receive Register (I2C0RD) I²C Bus 0 Slave Address Register (I2C0SA) I²C Bus 0 Transmit Data Register (I2C0TD) I²C Bus 0 Control Register (I2C0CON) I²C Bus 0 Mode Register (I2C0MOD) I²C Bus 0 Status Register (I2C0STAT) Corription of Operation Communication Operating Mode .1 Start Condition2 Repeated Condition                                                                                                                                                                                               | 14-114-114-114-214-314-414-514-714-914-9 |

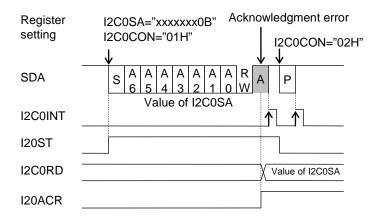

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>14.2.7<br>14.3 De<br>14.3.1<br>14.3.1<br>14.3.1                                                                                                     | Features Configuration List of Pins Coription of Registers List of Registers I²C Bus 0 Receive Register (I2C0RD) I²C Bus 0 Slave Address Register (I2C0SA) I²C Bus 0 Transmit Data Register (I2C0TD) I²C Bus 0 Control Register (I2C0CON) I²C Bus 0 Mode Register (I2C0MOD) I²C Bus 0 Status Register (I2C0STAT) Coription of Operation Communication Operating Mode .1 Start Condition .2 Repeated Condition .3 Slave Address Transmit Mode.                                                                                                                                                               | 14-114-114-114-214-314-414-514-814-914-9 |

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>14.2.7<br>14.3 De<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1                                                                                           | Features Configuration List of Pins Scription of Registers List of Registers I²C Bus 0 Receive Register (I2C0RD) I²C Bus 0 Slave Address Register (I2C0SA) I²C Bus 0 Transmit Data Register (I2C0TD) I²C Bus 0 Control Register (I2C0CON) I²C Bus 0 Mode Register (I2C0MOD) I²C Bus 0 Status Register (I2C0STAT) Scription of Operation Communication Operating Mode 1 Start Condition 2 Repeated Condition 2 Repeated Condition 3 Slave Address Transmit Mode 4 Data Transmit Mode                                                                                                                         |                                          |

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>14.2.7<br>14.3 De<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1                                                                                 | Features  Configuration  List of Pins  Cirption of Registers  List of Registers  1 <sup>2</sup> C Bus 0 Receive Register (I2C0RD)  1 <sup>2</sup> C Bus 0 Slave Address Register (I2C0TD)  1 <sup>2</sup> C Bus 0 Transmit Data Register (I2C0TD)  1 <sup>2</sup> C Bus 0 Control Register (I2C0CON)  1 <sup>2</sup> C Bus 0 Mode Register (I2C0MOD)  1 <sup>2</sup> C Bus 0 Status Register (I2C0STAT)  Corription of Operation  Communication Operating Mode  1 Start Condition  2 Repeated Condition  3 Slave Address Transmit Mode  4 Data Transmit Mode  5 Data Receive Mode                           |                                          |

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>14.2.7<br>14.3 De<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1                                                                       | Features Configuration List of Pins Coription of Registers List of Registers  1²C Bus 0 Receive Register (I2C0RD)  1²C Bus 0 Slave Address Register (I2C0TD)  1²C Bus 0 Transmit Data Register (I2C0TD)  1²C Bus 0 Control Register (I2C0CON)  1²C Bus 0 Mode Register (I2C0MOD)  1²C Bus 0 Status Register (I2C0STAT)  Corription of Operation Communication Operating Mode  1 Start Condition  2 Repeated Condition  3 Slave Address Transmit Mode  4 Data Transmit Mode  5 Data Receive Mode  6 Control Register Setting Wait State                                                                      |                                          |

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>14.2.7<br>14.3 De<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1                                                             | Features Configuration List of Pins Coription of Registers List of Registers  List of Registers  L'C Bus 0 Receive Register (I2C0RD)  1'C Bus 0 Slave Address Register (I2C0TD)  1'C Bus 0 Transmit Data Register (I2C0TD)  1'C Bus 0 Control Register (I2C0CON)  1'C Bus 0 Mode Register (I2C0MOD)  1'C Bus 0 Status Register (I2C0STAT)  Coription of Operation  Communication Operating Mode  1 Start Condition  2 Repeated Condition  3 Slave Address Transmit Mode  4 Data Transmit Mode  5 Data Receive Mode  6 Control Register Setting Wait State  7 Stop Condition                                 |                                          |

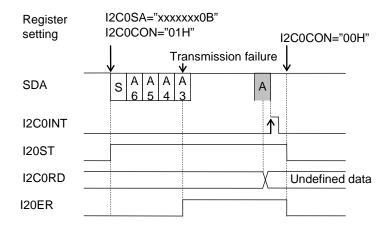

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>14.2.7<br>14.3 De<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1                                         | Features Configuration List of Pins Coription of Registers List of Registers  List of Registers  1°C Bus 0 Receive Register (I2C0RD)  1°C Bus 0 Slave Address Register (I2C0TD)  1°C Bus 0 Transmit Data Register (I2C0TD)  1°C Bus 0 Control Register (I2C0CON)  1°C Bus 0 Mode Register (I2C0MOD)  1°C Bus 0 Status Register (I2C0STAT)  Coription of Operation  Communication Operating Mode  1 Start Condition  2 Repeated Condition  3 Slave Address Transmit Mode  4 Data Transmit Mode  5 Data Receive Mode  6 Control Register Setting Wait State  7 Stop Condition  Communication Operation Timing |                                          |

| 14.1.2<br>14.1.3<br>14.2 De<br>14.2.1<br>14.2.2<br>14.2.3<br>14.2.4<br>14.2.5<br>14.2.6<br>14.2.7<br>14.3 De<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.1<br>14.3.3 | Features Configuration List of Pins Coription of Registers List of Registers  List of Registers  L'C Bus 0 Receive Register (I2C0RD)  1'C Bus 0 Slave Address Register (I2C0TD)  1'C Bus 0 Transmit Data Register (I2C0TD)  1'C Bus 0 Control Register (I2C0CON)  1'C Bus 0 Mode Register (I2C0MOD)  1'C Bus 0 Status Register (I2C0STAT)  Coription of Operation  Communication Operating Mode  1 Start Condition  2 Repeated Condition  3 Slave Address Transmit Mode  4 Data Transmit Mode  5 Data Receive Mode  6 Control Register Setting Wait State  7 Stop Condition                                 | 14-1                                     |

| Chapter 1 | 5 |

|-----------|---|

|-----------|---|

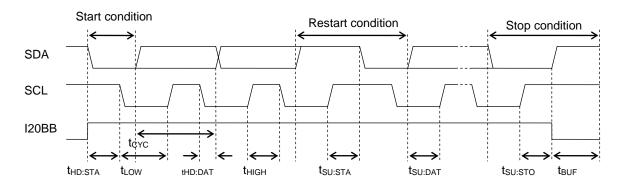

|                   | Pinerview                                                    |      |

|-------------------|--------------------------------------------------------------|------|

| 15.1 Ov<br>15.1.1 | Features                                                     |      |

| 15.1.1            |                                                              |      |

| 15.1.2            | Configuration                                                |      |

|                   | List of Pinsscription of Registers                           |      |

| 15.2 De           | List of Registers                                            |      |

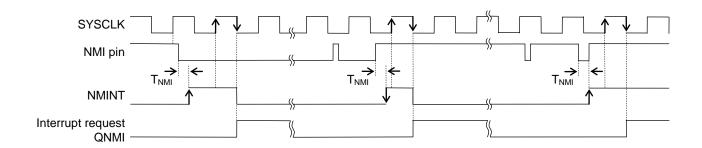

| 15.2.1            | NMI Data Register (NMID)                                     |      |

| 15.2.2            | NMI Control Register (NMICON)                                |      |

|                   | scription of Operation                                       |      |

| 15.3.1            | Interrupt Request                                            |      |

| Chapter 1         | 6                                                            |      |

|                   | )                                                            | 16-1 |

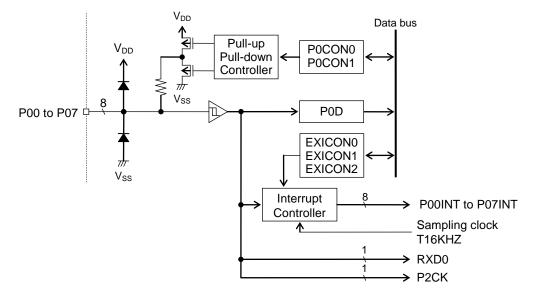

|                   | erview                                                       |      |

| 16.1.1            | Features                                                     |      |

| 16.1.2            | Configuration                                                |      |

| 16.1.3            | List of Pins                                                 |      |

|                   | scription of Registers                                       |      |

| 16.2.1            | List of Registers                                            |      |

| 16.2.2            | Port 0 Data Register (P0D)                                   |      |

| 16.2.3            | Port 0 Control Registers 0, 1 (P0CON0, P0CON1)               |      |

| 16.2.4            | External Interrupt Control Registers 0, 1 (EXICON0, EXICON1) |      |

| 16.2.5            | External Interrupt Control Register 2 (EXICON2)              |      |

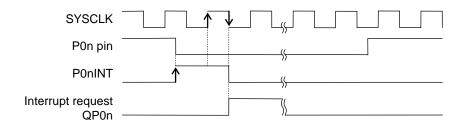

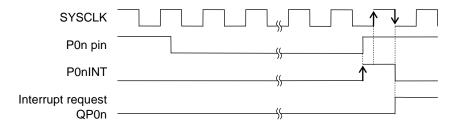

|                   | scription of Operation                                       |      |

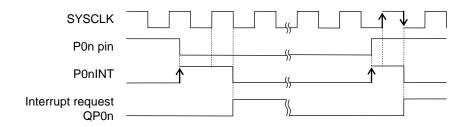

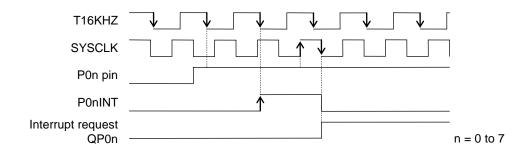

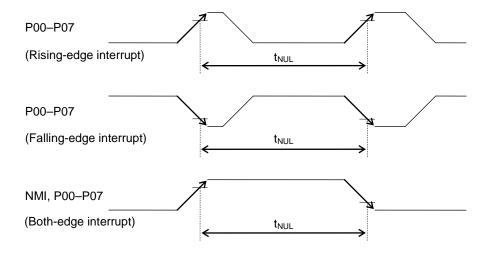

| 16.3.1            | External Interrupt                                           |      |

| 16.3.2            | Interrupt Request                                            |      |

| Chapter 1         | 7                                                            | 17-1 |

|                   | erview                                                       |      |

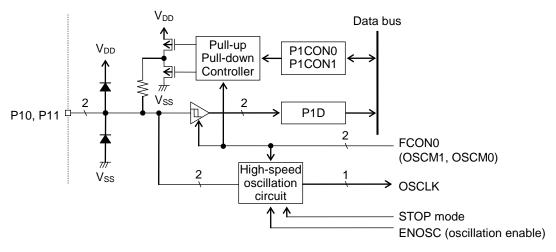

| 17.1.1            | Features                                                     |      |

| 17.1.2            | Configuration                                                |      |

| 17.1.3            | List of Pins                                                 |      |

|                   | scription of Registers                                       |      |

| 17.2.1            | List of Registers                                            |      |

| 17.2.2            | Port 1 Data Register (P1D)                                   |      |

| 17.2.3            | Port 1 Control Registers 0, 1 (P1CON0, P1CON1)               |      |

|                   | scription of Operation                                       |      |

| 17.3.1            | Input Port Function                                          |      |

| 17.3.2            | Secondary Function                                           | 17-5 |

| Chapter 1         | 8                                                            |      |

| 18. Port 2        | 2                                                            | 18-1 |

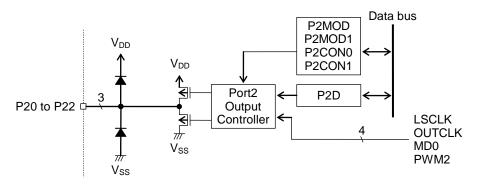

| 18.1 Ov           | erview                                                       | 18-1 |

| 18.1.1            | Features                                                     | 18-1 |

| 18.1.2            | Configuration                                                | 18-1 |

| 18.1.3            | List of Pins                                                 |      |

| 18.2 De           | scription of Registers                                       | 18-2 |

| 18.2.1            | List of Registers                                            |      |

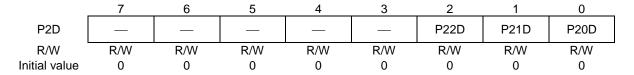

| 18.2.2            | Port 2 Data Register (P2D)                                   | 18-3 |

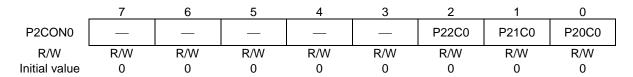

| 18.2.3            | Port 2 control registers 0, 1 (P2CON0, P2CON1)               | 18-4 |

| 18.2.4            | Port 2 Mode Register, Port 2 Mode Register1 (P2MOD, P2MOD1)  | 18-5 |

| 18.2.5            | Port 2 Mode Register 2 (P2MOD2)                              |      |

| 18.3 De           | scription of Operation                                       | 18-8 |

|                   |                                                              |      |

$\begin{array}{c} ML610Q428/ML610Q429 \; User's \; Manual \\ Contents \end{array}$

| 18.3.1<br>18.3.2 | Output Port Function                                         |       |

|------------------|--------------------------------------------------------------|-------|

| Chapter 1        | 9                                                            |       |

| 19. Port         | 3                                                            | 19-1  |

|                  | verview                                                      |       |

| 19.1.1           | Features                                                     | 19-1  |

| 19.1.2           | Configuration                                                | 19-1  |

| 19.1.3           | List of Pins                                                 | 19-2  |

| 19.2 De          | escription of Registers                                      | 19-3  |

| 19.2.1           | List of Registers                                            |       |

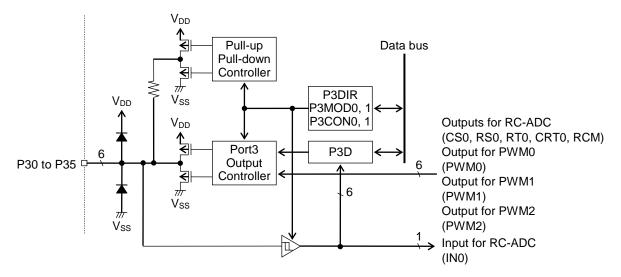

| 19.2.2           | Port 3 data register (P3D)                                   |       |

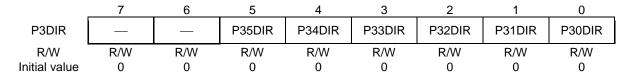

| 19.2.3           | Port 3 Direction Register (P3DIR)                            |       |

| 19.2.4           | Port 3 control registers 0, 1 (P3CON0, P3CON1)               |       |

| 19.2.5           | Port 3 mode registers 0, 1 (P3MOD0, P3MOD1)                  |       |

|                  | escription of Operation                                      |       |

| 19.3.1           | Input/Output Port Functions                                  |       |

| 19.3.2           | Secondary and Tertiary Functions                             | 19-10 |

| Chapter 2        | 20                                                           |       |

|                  | 4                                                            |       |

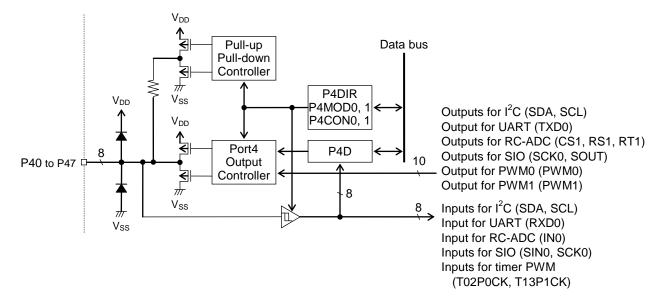

| 20.1 Ov          | verview                                                      |       |

| 20.1.1           | Features                                                     |       |

| 20.1.2           | Configuration                                                |       |

| 20.1.3           | List of Pins                                                 |       |

|                  | escription of Registers                                      |       |

| 20.2.1           | List of Registers                                            |       |

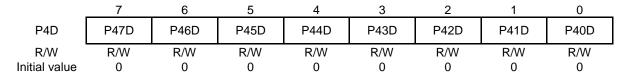

| 20.2.2           | Port 4 Data Register (P4D)                                   |       |

| 20.2.3           | Port 4 Direction Register (P4DIR)                            |       |

| 20.2.4           | Port 4 Control Registers 0, 1 (P4CON0, P4CON1)               |       |

| 20.2.5           | Port 4 Mode Registers 0, 1 (P4MOD0, P4MOD1)                  |       |

|                  | escription of Operation                                      |       |

| 20.3.1<br>20.3.2 | Input/Output Port Functions Secondary and Tertiary Functions |       |

|                  |                                                              | 20-11 |

| Chapter 2        |                                                              |       |

|                  | A                                                            |       |

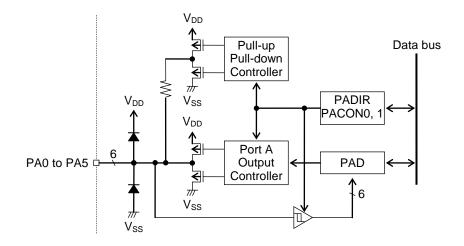

|                  | /erview                                                      |       |

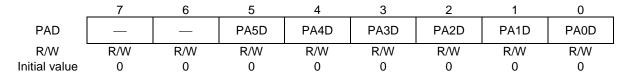

| 21.1.1<br>21.1.2 | Features                                                     |       |